如果注重的是“9nV/Sqrt(Hz)@1kHz”的话……普通JFET运放这个参数就优于楼主列出的了。

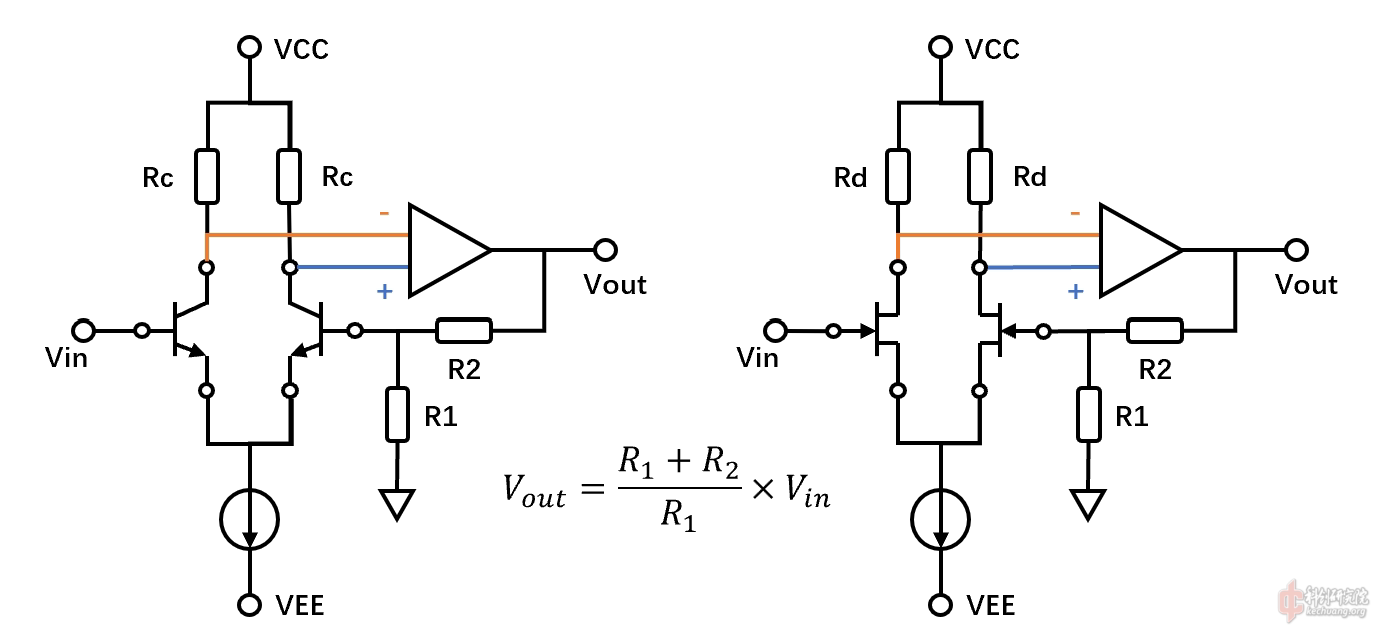

结型场效应管是一种小众的电路元件,近年来生产规模持续缩小,连专业人士都容易将其当做MOS场效应管。但在特定的小众应用领域,JFET管具有不可替代的优势,比如我关注的低噪声、低失调放大电路。这是因为,分立JFET管可以设计更大的硅片面积,并配置更高的工作电流,不受封装方案的影响。另一方面,如果整个电路都使用JFET管等分立元件,则电路会过于复杂难以设计和调整,所以会用操作简单的运放来代替这部分电路。综合这两点考虑,JFET管+运放会采用下面的电路。

上图中,左图是BJT管+运放组成的放大电路,右图才是JFET管+运放组成的电路。从应用上看,BJT管往往有更低的噪声和失调电压,但输入电阻往往远小于JFET管,对准确测量电压的要求往往不太能满足。作为结果,JFET管成为万用表的主要选型方案,下面列举一些我收集的典型万用表选型方案:

万用表型号 | 特性 | 前端元件型号 |

| Keysight 3458 | 八位半高分辨万用表 | NPD5564(同2N5564) |

| Keysight 34401 | 六位半高分辨万用表 | U401 |

| Keysight 34420 | 七位半纳伏表,底噪8nV P-P | Interfet IF3602 |

| Keithley 182 | 六位半纳伏表,底噪15nV P-P | 编号TG-255,可能是Toshiba 2SK162 |

| Keysight 2182 | 七位半纳伏表,底噪6nV P-P | Toshiba 2SK170 + LM394 后改为Linear System LSK170 + LM394 |

| Datron 1281 | 八位半高分辨万用表 | Siliconix U401 |

| Solartron 7081 | 八位半高分辨万用表 | WD401(不明元件) |

电路方案与测试结果

我在另一篇文章里写过JFET管+运放组成放大电路的方案与指标:XXXXXXXXXXXXXXXXXXXXXXXX/t/89239。但是这次实验的指标不太理想,主要有下面几个问题:

电流源模块里,BJT管上的分压过高(约为8.5V-2.5V=6V),导致引入额外噪声。将该电压配置在3.5V以下就比较合适,几乎不引入额外噪声。

数据处理的FFT算法有问题,似乎是没有加窗函数、导致低频噪声的旁瓣过渡扩展,表现为低频噪声延伸到1kHz以上。另外,高频噪声也被扩大了2倍,但原因还不清楚。目前调用了Python的scipy的.signal.welch方法,使用最小4阶Blackman-Harries窗函数处理数据,明显改善了频谱测量结果。

调整失调电压的源极电阻RS中采用了可调电阻,但电阻每次调整后都需要1min以上的稳定时间,在此期间失调电压会持续变化,导致调压不准确。这次改用开关电阻阵列+可调电阻的方案来处理电压失调,几乎消除了可调电阻稳定过程对测量的影响。

此外,我还采用了这些电路设计方案,但似乎没有改善灵敏度指标。这里将这些方案列举出来,以供大家分析。

在漏极电阻RD上加电流镜电路,迫使两只JFET管上流过相同的电流。从结果上看,这类似于增加RD电阻的阻值,进一步抑制后端运放对噪声的影响。这个功能在我这里似乎没发挥作用,可能是因为我用的OP07CP运放仅有10nV/Sqrt(Hz)的电压噪声密度,而阻值RD普遍选得较大,因此运放噪声不占主要因素。

在漏极电阻部分加上Cascode电路,配合参考电压源,使得JFET管的VDS电压始终维持不变。这似乎能增加放大电路的工作带宽,但我并不关心带宽,所以并未专门测试。

一些方案已被证明无效,具体内容如下:

电流镜和Cascode单路包含三极管元件,增强这些三极管的对称性、或降低这些三极管的噪声是无效的。我用THAT340三极管阵列代替了9014、9015等普通三极管,但噪声并无显著变化。

空间电磁辐射似乎具有电流源的性质,在高阻抗元件上的干扰电压会更大,而这恰好是JFET管的特征。我在输入端并联1只10MΩ电阻到GND,已经极大降低输入阻抗,但似乎没啥影响。

按照上述方案,我做了一些电路板进行测试。下图是一只使用2SK170V的放大电路,设计在6mA的IDS下工作,使用了电流镜和Cascode电路,改用BJT管搭建电流源,但继续用可调电阻在RS上调整失调电压。该电路的实物和测试结果如下图所示,可见电压发生指数漂移,噪声水平约为5nV/Sqrt(Hz)。

然而,如果继续使用可调电阻,则输出电压是不可能稳定下来的。下图就是一个典型案例,输入电压在4s的时间尺度上变化了3uV,且看起来像随机波动,而这只可能来源于可调电阻。

值得一提的是,该电路是是在没有屏蔽盒的条件下测的噪声数据,因此出现了一大堆空间电磁噪声在特定频率上产生的噪声尖峰。之前的电路板则是在金属盒内做的测试(但没有用内层金属壳+电压源做成主动屏蔽),这些噪声明显小了许多。

将可调电阻方案换成开关电阻阵列+可调电阻方案,结果如下图所示。可以看出,电压的长期波动几乎消失,说明这一步改对了,可调电阻确实是输出电压异常波动的源头或关键节点。

但是失调电压变化的问题并未根绝。具体来说,当我把电路从桌子上装进金属盒时,输出电压就会急剧改变,产生大约400uV的电压变化,我不知道这是热电势、JFET管温漂还是PCB应力变化导致的,但这肯定不是电子学应当解决的问题,我只能建议避免在测试中移动电路板。我抓拍了一段电压变化的数据,这个电压变化似乎也有指数变化的特征。

我在一块电路板中,将IDS从6mA改成了10mA,使得输出电压从4nV/Sqrt(Hz)降低到3nV/Sqrt(Hz),下图是这次测试的测试结果。

我还尝试了2SK129。LSK389C这两种型号的JFET管,其中LSK389C的结果如下图所示,噪声水平也在3nV/Sqrt(Hz)左右,跟2SK170差不多。

2SK129的测试结果就不太行。该电路的输出电压噪声约为9nV/Sqrt(Hz),而且低频噪声明显延伸到1kHz以上,如下图所示,估计该型号的JFET管性能非常一般。

目前来看,JFET管+运放混合电路的失调电压问题已经基本解决,下一步应当优化噪声密度(特指频率较高位置的噪声密度,如1kHz)和低频噪声转折频率,目前考虑的方案有这些:

我一直用加法器方案来细调失调电压,因此输入端总是串联1只10Ω左右的金属膜电阻,该电阻可能是噪声的主要来源。目前来看,电阻开关阵列+可调电阻的方案有很高的调控精度,不需要继续使用加法器,可以去掉这部分电路。

我一直没考虑环境噪声的影响,如果环境中存在低频电磁噪声,就能解释噪声密度偏高的问题。之后我会尝试去噪声较低的环境进行测试(比如隔壁的公园之类),看看指标是否发生改变。

如果注重的是“9nV/Sqrt(Hz)@1kHz”的话……普通JFET运放这个参数就优于楼主列出的了...

赞同,这也是我头疼的问题。

现代电子元件里,低噪声运放的噪声密度标称值能达到0.8nV/Sqrt(Hz)左右,比如LT1028/LT1128、OPA211之类的,对应大概10uV的失调电压;低失调运放能做到2.5uV的失调电压,噪声也能做到5nV/Sqrt(Hz)左右,比如ADA4528、ADA4522、ICL7650之类。这类运放用的是BJT前级,噪声和失调性能相当漂亮,只是输入阻抗、输入偏置电流/失调电流稍微差一点,大多数时候直接用就可以了。

具体到JFET运放,我的调研就不太够,目前对比的是TI的OPA392。该元件的输入偏置电流是10fA,多半是JFET管前级结构(不排除超Beta型BJT管前级的可能性,但MOS管应该不可能),对应4.4nV/Sqrt(Hz) @ 10kHz的噪声和10uV的失调电压。我目前能做到3nV/Sqrt(Hz) @ 1kHz,比这个要稍微好一点,对我自己来说还算是解释的过去。

让我头疼的是,2SK170的噪声标称值是0.95nV/Sqrt(Hz) @ 1kHz,考虑差分方案的话应该在1.33nV/Sqrt(Hz)左右,算是我的方案的理论值。我才做到3nV/Sqrt(Hz),说明有5倍理论值左右的噪声源在碍事,真是越想越亏。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

您要做到这么高境界的话,要考虑很多问题,比如这么高输入阻抗就需要考虑PCB板材的介电常数,输入端的漏电电阻,线路板表面的清洁程度,湿度影响,阻焊层产生的静电噪声等等

200字以内,仅用于支线交流,主线讨论请采用回复功能。

前端JFET,八位8508和R6581都用了U401,七位7510用了LSK389B,我一直有一个疑问,围绕噪声这一指标,七位半和八位半的前端放大的噪声指标要求是多少?器件的噪声指标给的是噪声频谱密度,而实际测量是以时间为单位的,当测量DC信号时前端放大的噪声会被模拟积分器积分,按照8588测量时间10s计算,仿真计算前端放大在0.1Hz-10Hz的频带内的RMS噪声会超出产品宣传的1nV分辨率,这点我一直想不明白,前端放大器的噪声做到什么样的指标能满足七位八位表的需求?

200字以内,仅用于支线交流,主线讨论请采用回复功能。