这两天在测试AD9850数字频率合成器模块,该DDS可以在125MHz晶振下稳定输出1Hz-40MHz的正弦波信号,频率分辩率为0.03Hz,换而言之,在整个输出范围内,频率可以以0.03Hz为步进单位改变。

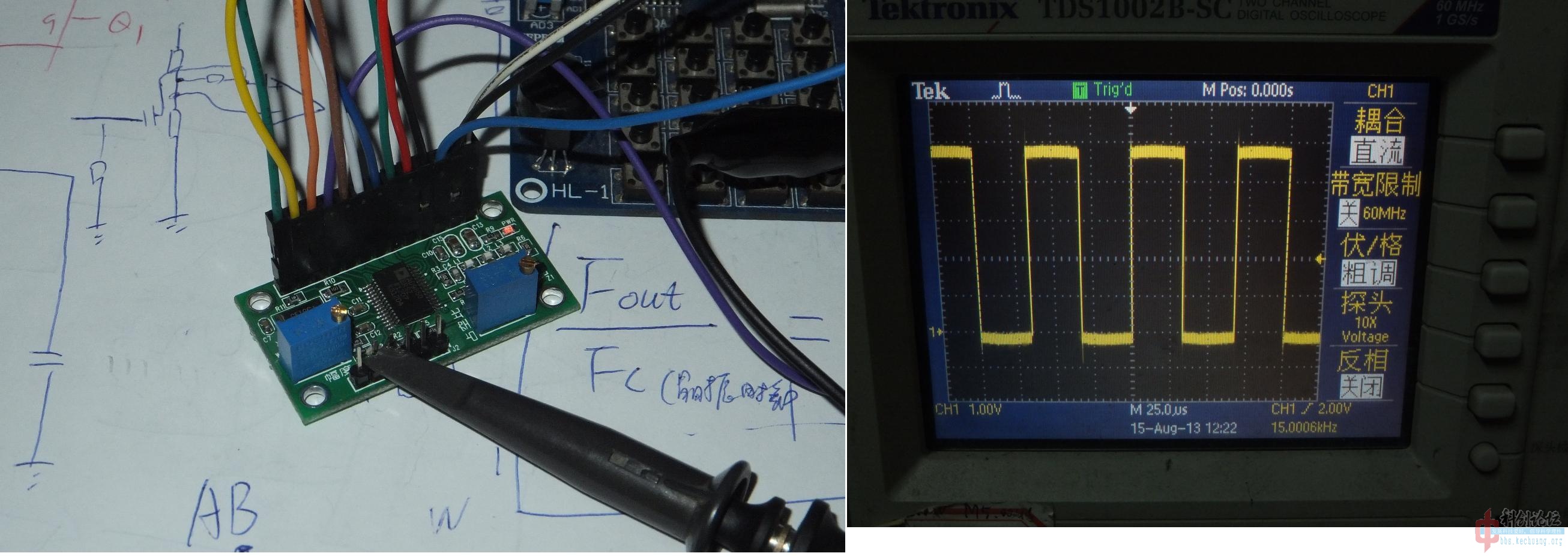

以下是测试的图片和使用的函数。实际模块输出信号已由9850内置的高速比较器整形为方波输出。

![合并图.jpg]()

![1.5M.jpg]()

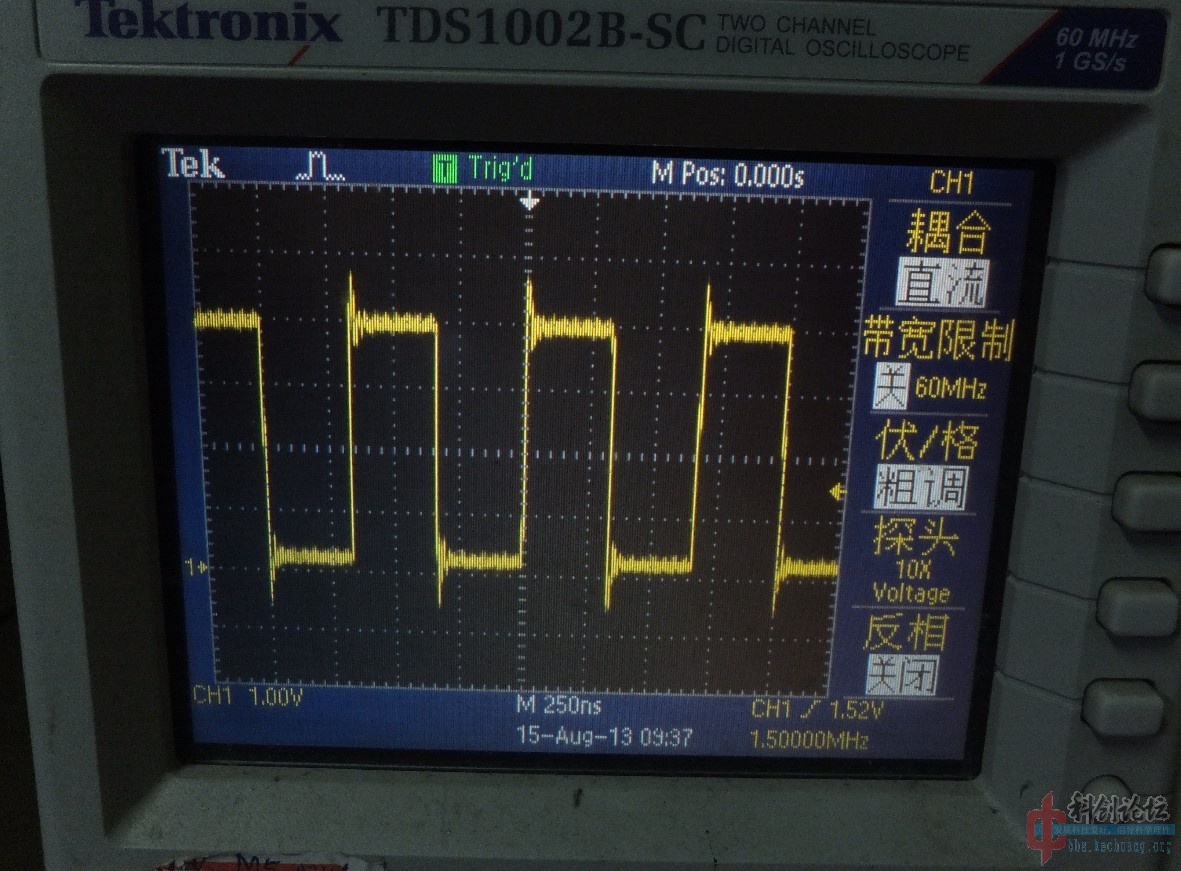

顺便上一个1.5MHz的测试图,由于晶振误差,实际是在函数里面写了一个1.49999MHz的值才输出此信号

测试程序里面可以任意改变函数的输出频率值(当然是在范围内的)。图中程序是以15000.5Hz为输出频率,实际因为晶振有些许误差,导致频率输出有误差。

以下是分享的程序代码(完整简洁的并口驱动代码):

//硬件连接使用P1口的8位并口与AD9851的8位并口直接连接

#include <reg51.h>

#define ulong unsigned long

sbit wclk=P3^0; //定义数据传输控制位

sbit ud=P3^1; //定义频率刷新控制位

sbit reset=P3^2; //定义复位端口

ulong temp; //频率控制字值

void output(float);

void main()

{

P3=0x00[s:9]1=0x00;

reset=1;reset=1;reset=0; //复位模块

output(15000.5); //以输出15000.5Hz测试,实际输出15000.6Hz,经查是由晶振误差引起。 想要输出什么频率直接在表达式里面写就行

while(1);

}

void output(float temp0) //频率输出函数。这里采用浮点函数,因为输出频率需要精确到小数点后

{

temp=temp0*34.35973837; //计算控制字值temp,34.35...是由2的32次方除以晶振频率(4294967296/125000000)得来

P1=0x00;wclk=1;wclk=0; //设定工作模式等

P1=temp/16777216;wclk=1;wclk=0; //对控制字值除以二进制的1 00000000 00000000 00000000求模送入控制字第一字节

P1=temp%16777216/65536;wclk=1;wclk=0; //对控制字值求余以后对下一字节求模送入第二字节

P1=temp%65536/256;wclk=1;wclk=0; //下一个字节

P1=temp%256;wclk=1;wclk=0; //最后一个字节

ud=1;ud=0; //刷新频率输出

}

顺便上一个1.5MHz的测试图,由于晶振误差,实际是在函数里面写了一个1.49999MHz的值才输出此信号

顺便上一个1.5MHz的测试图,由于晶振误差,实际是在函数里面写了一个1.49999MHz的值才输出此信号

200字以内,仅用于支线交流,主线讨论请采用回复功能。