本帖主要针对

https://www.kechuang.org/t/50374(下称帖1),

https://www.kechuang.org/t/50579(下称帖2)这2帖编写。

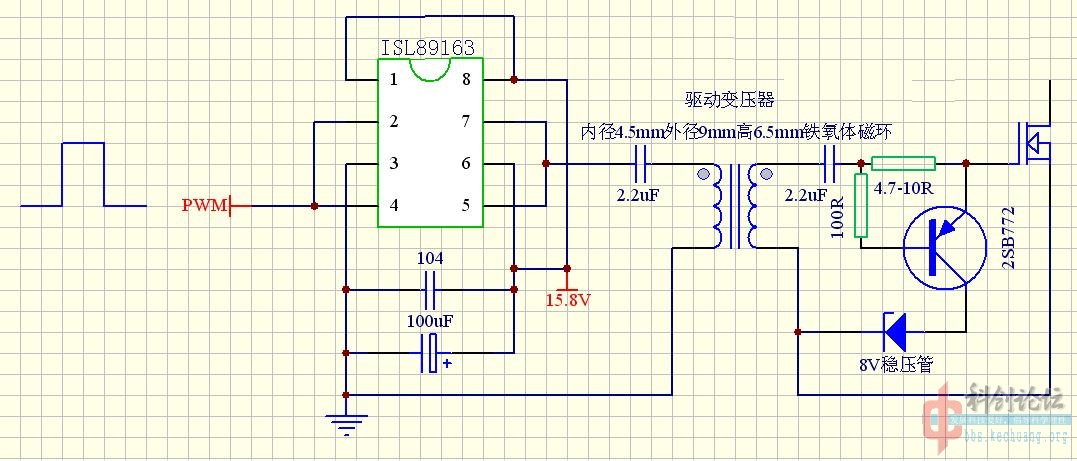

在帖1中,ehco大师主张驱动变压器的输出电流和功率要按驱动峰值电流和峰值功率设计,从而驱动变压器会很大,而且在帖2中列出了他所做的一套驱动的具体数据。本帖主张驱动变压器可以按输出平均电流和平均功率来设计,大家都知道驱动变压器的负载是电容性负载,而驱动变压器输出的是方波,驱动变压器的输出平均电流和平均功率非常小,所以驱动变压器可以做的非常小。

为此,本人专门做了一套驱动电路,和帖2中ehco兄的驱动做了详细的对比,以此来验证我的观点的正确性。

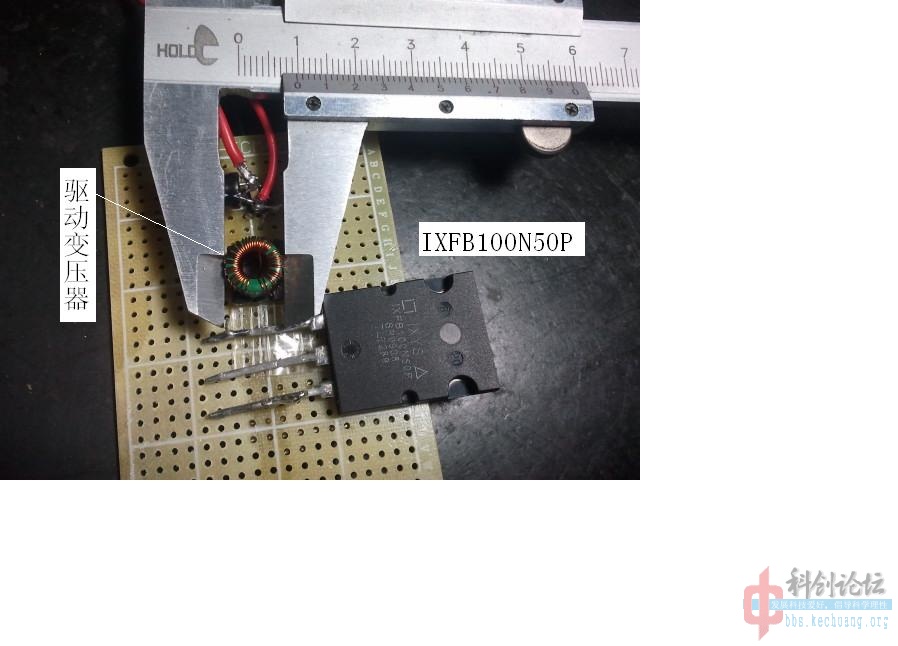

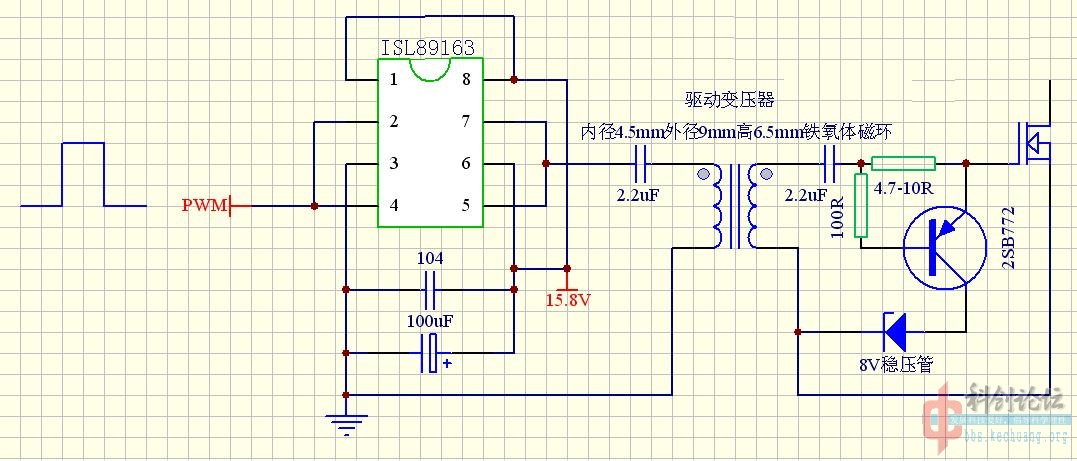

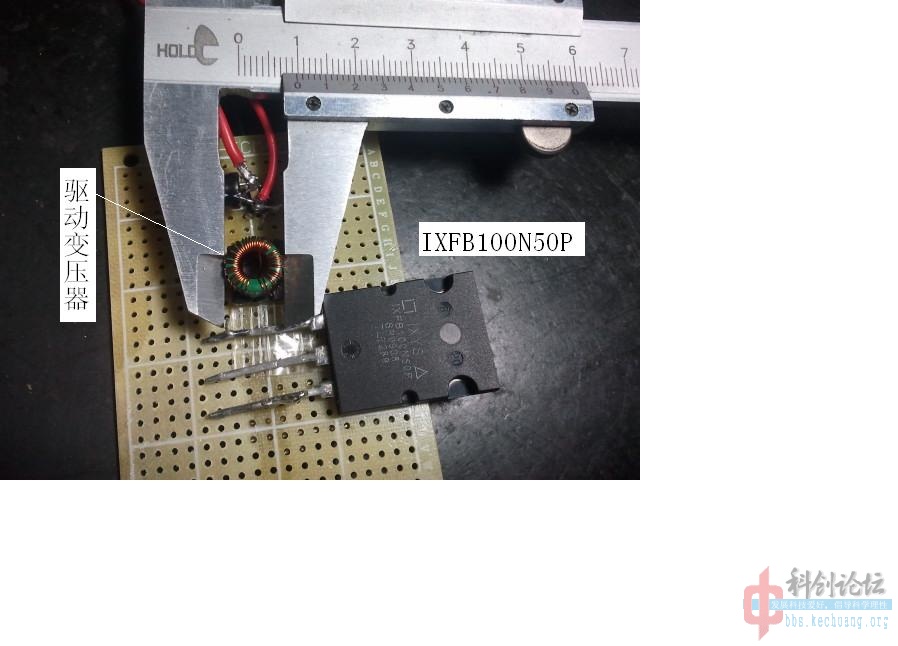

我的驱动变压器的磁芯是内径4.5mm外径9mm高6.5mm的铁氧体磁环,初级0.25mm漆包线15圈,次级0.25mm漆包线24圈,下面有我的驱动变压器的图片,从图片中可以看出整个变压器的直径只有9.5 mm。ehco兄的驱动变压器是罐形铁氧体,尺寸和绕组参数不详,但从图片来看体积不小于我的50倍!为了做准确的比较,驱动电压我做的和他的一样,正15V负8V。

负载 ehco兄的是场效应管2MI50F050,此管是500V50A的场效应管,GS电容典型值7.8纳法

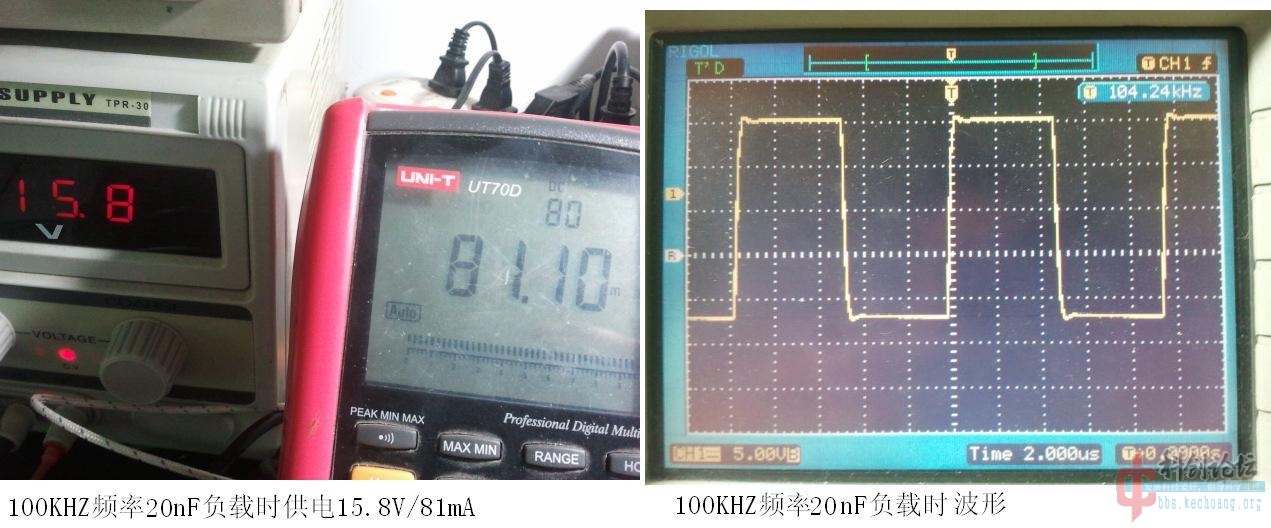

我实验两大小两种负载,大负载是IXFB100N50P场效应管,此管是500V100A的管子,GS电容典型值20纳法,是ehco实验的2.5倍。小负载本来想找和2MI50F050结电容相近的管子,但是一时找不到,就拿了一个10纳法的贴片电容,大家应该知道,场效应管的GS电容一般都有一个比较大的内阻,而贴片电容的内阻可是非常小的。驱动电路的负载电容内阻越小,Q值就越高,越容易振荡,而要抑制振荡就要串联比较的大驱动电阻,串联的电阻大了在负载电容上得到的上升和下降时间就会比较长,也就是说电容内阻越小越难驱动。

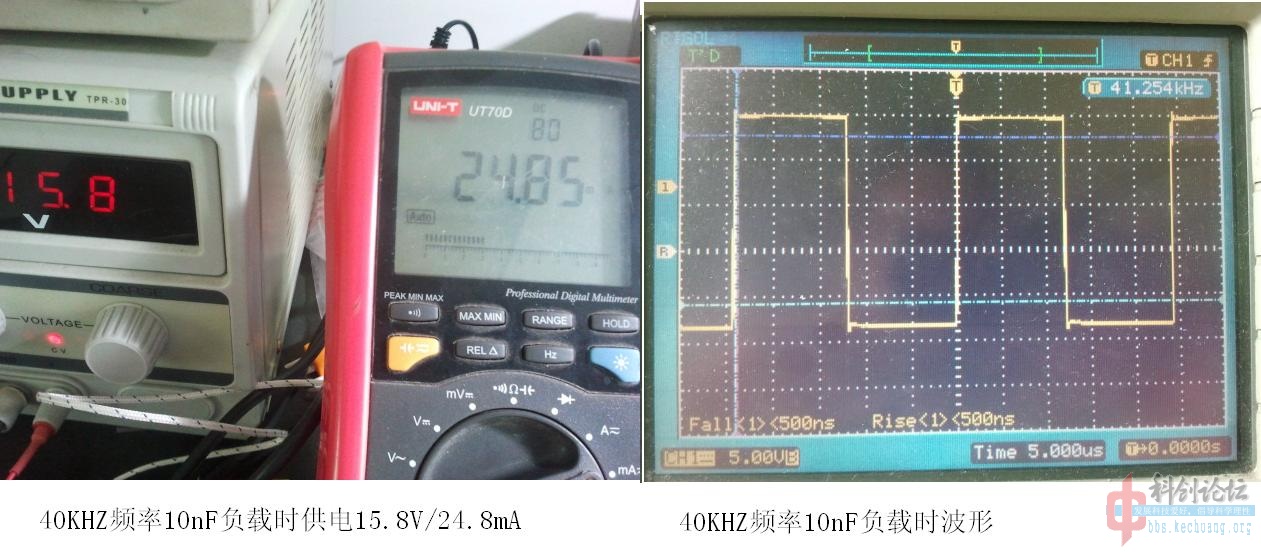

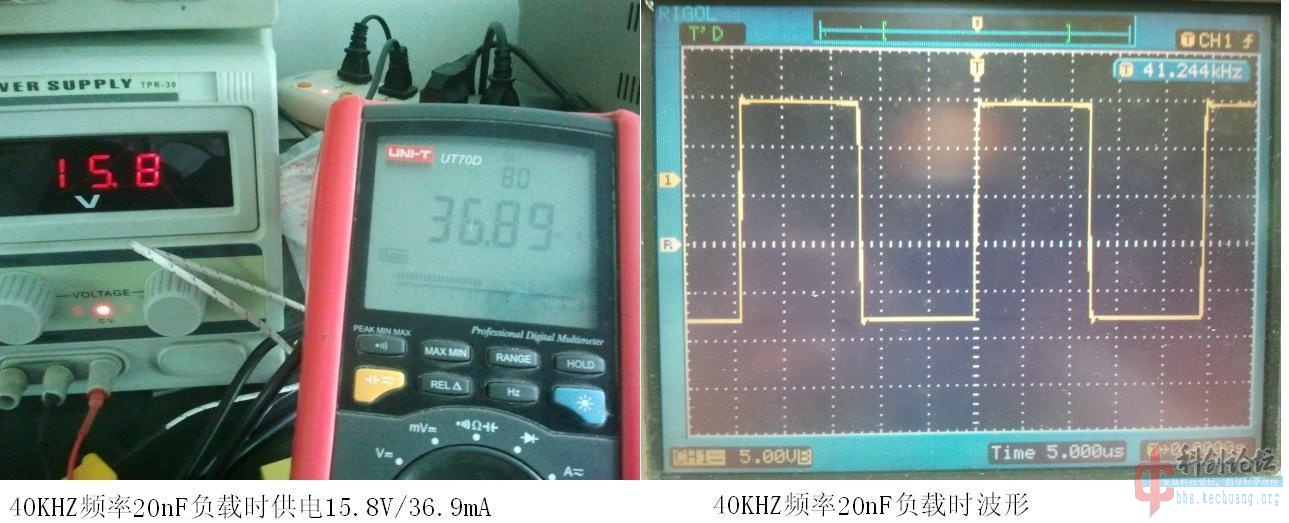

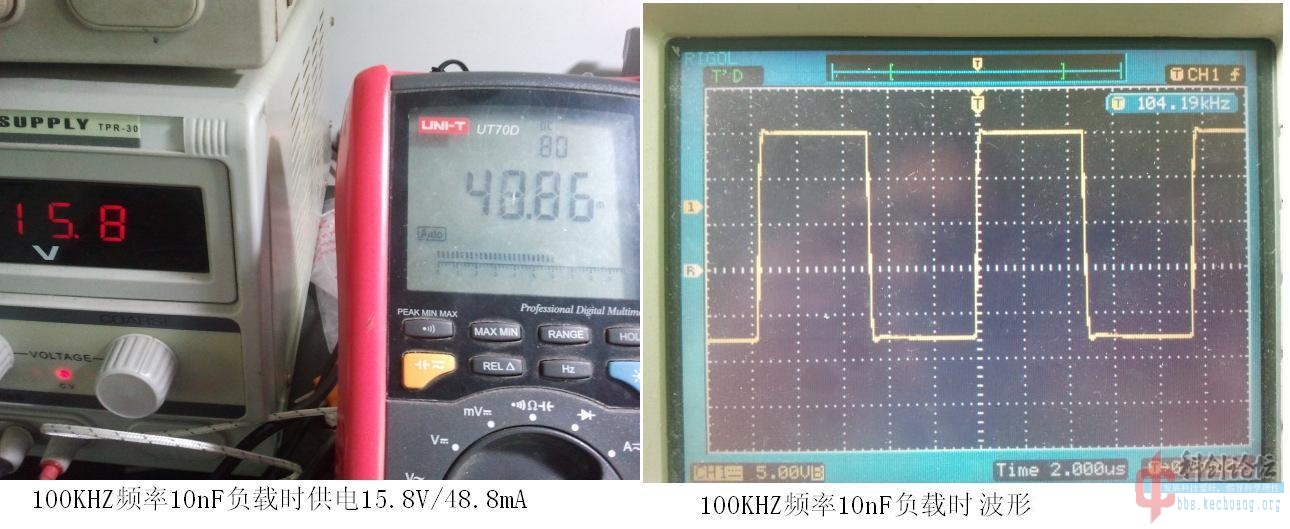

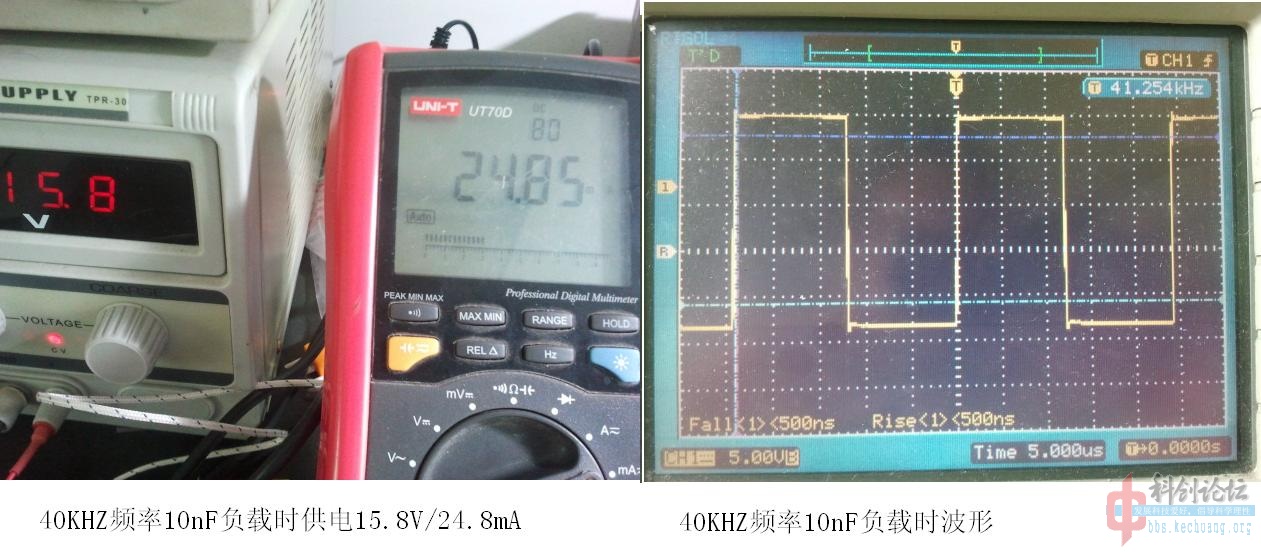

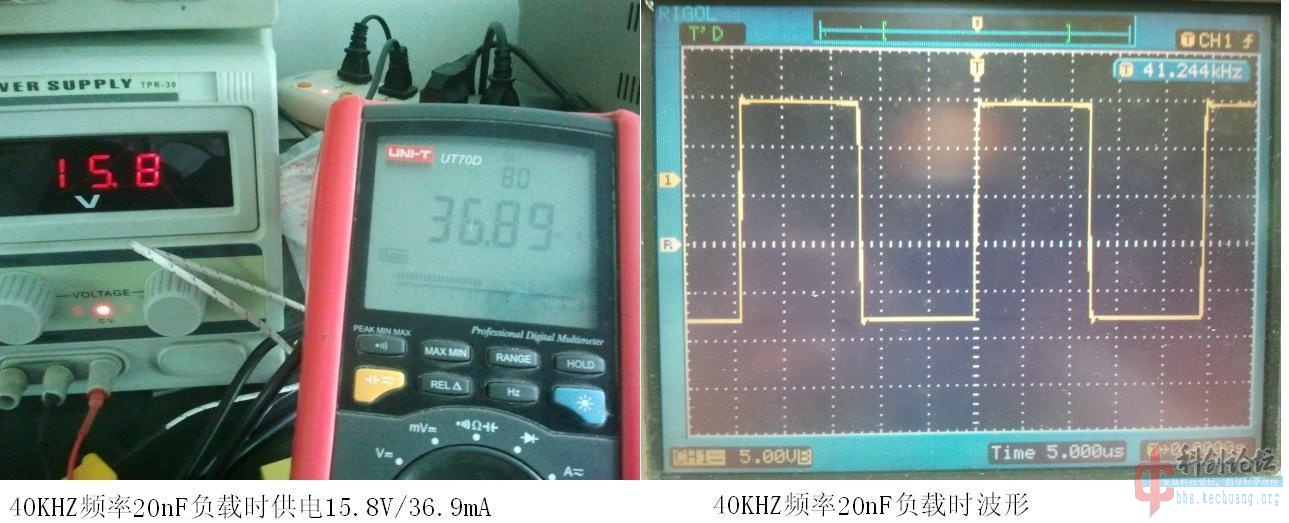

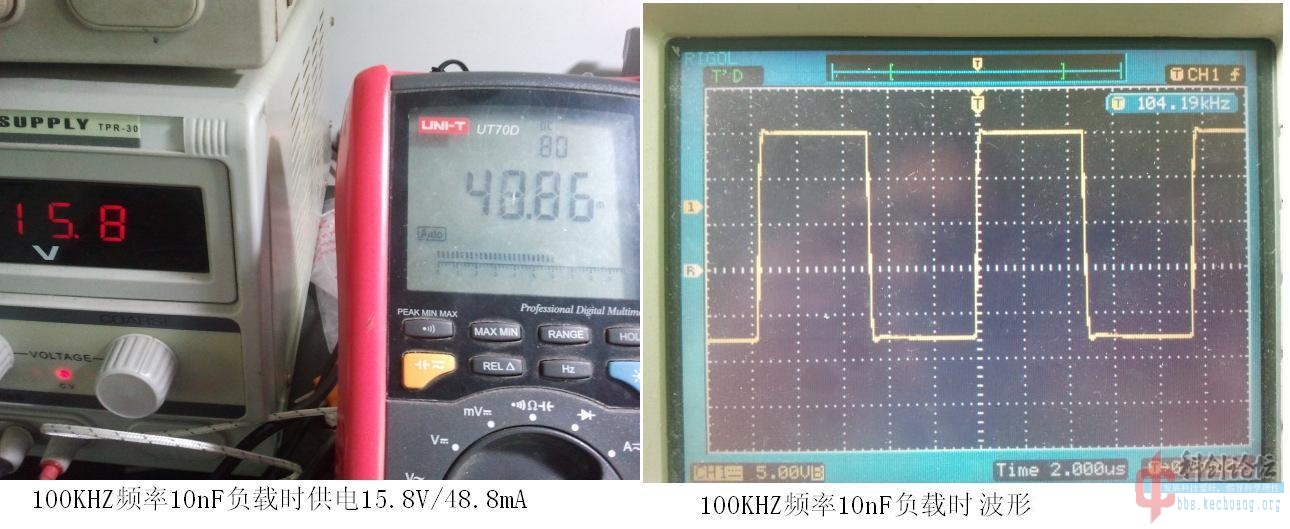

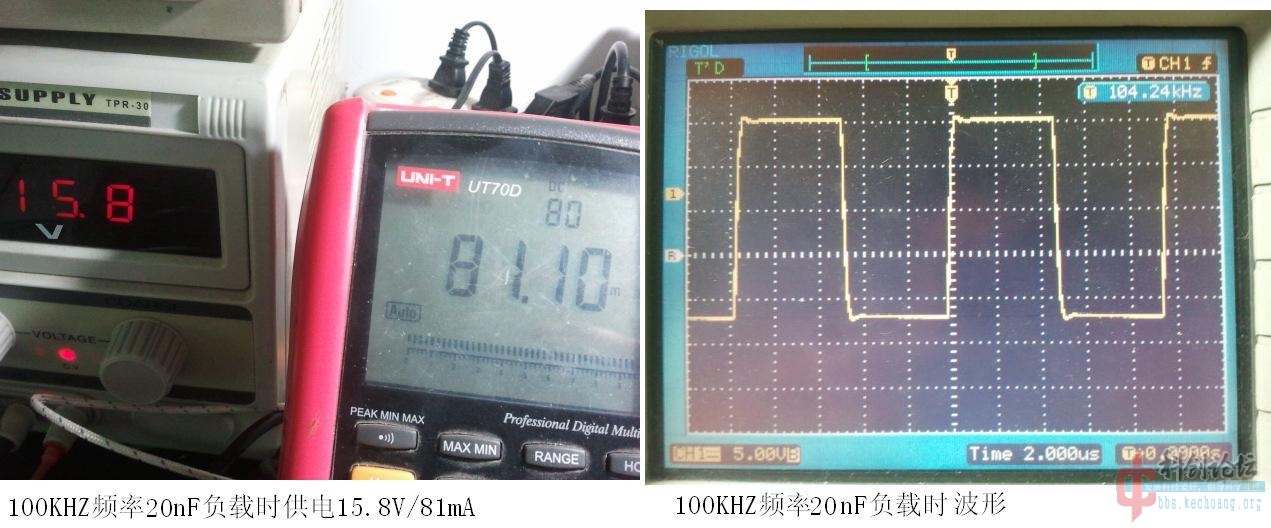

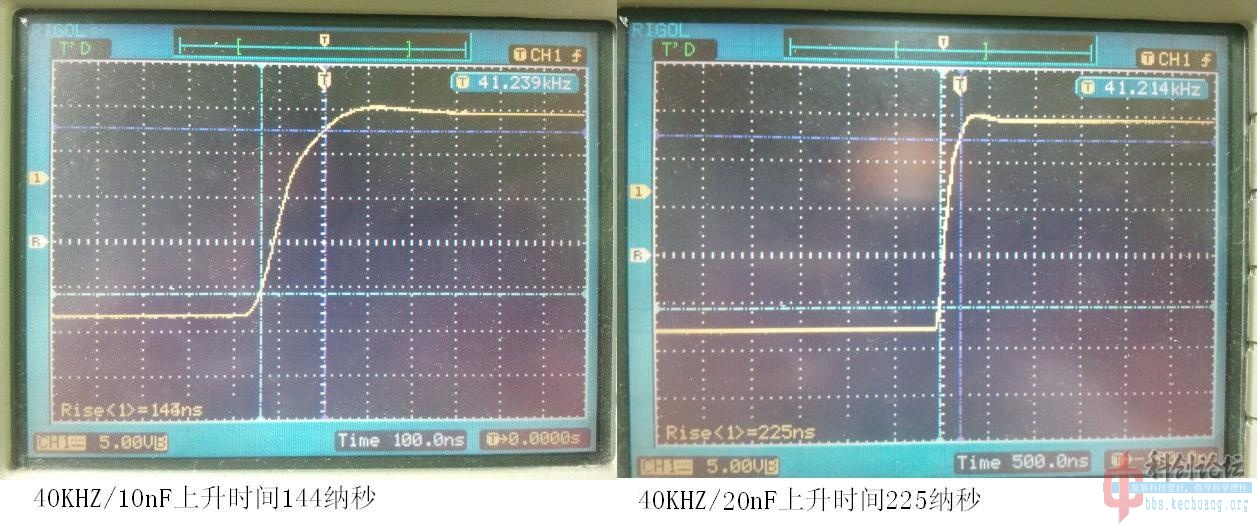

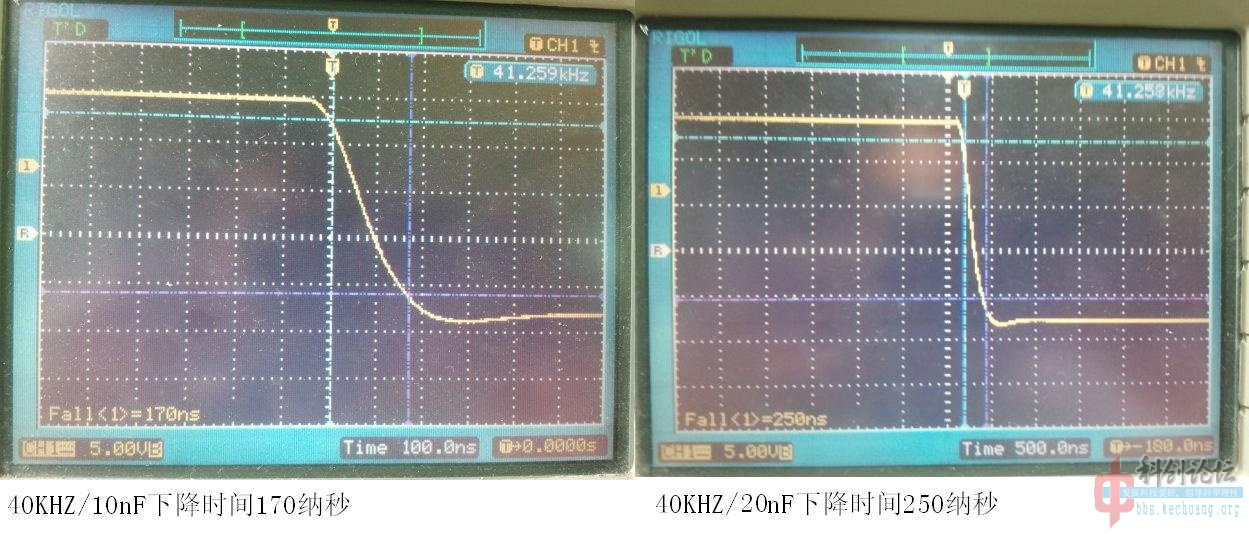

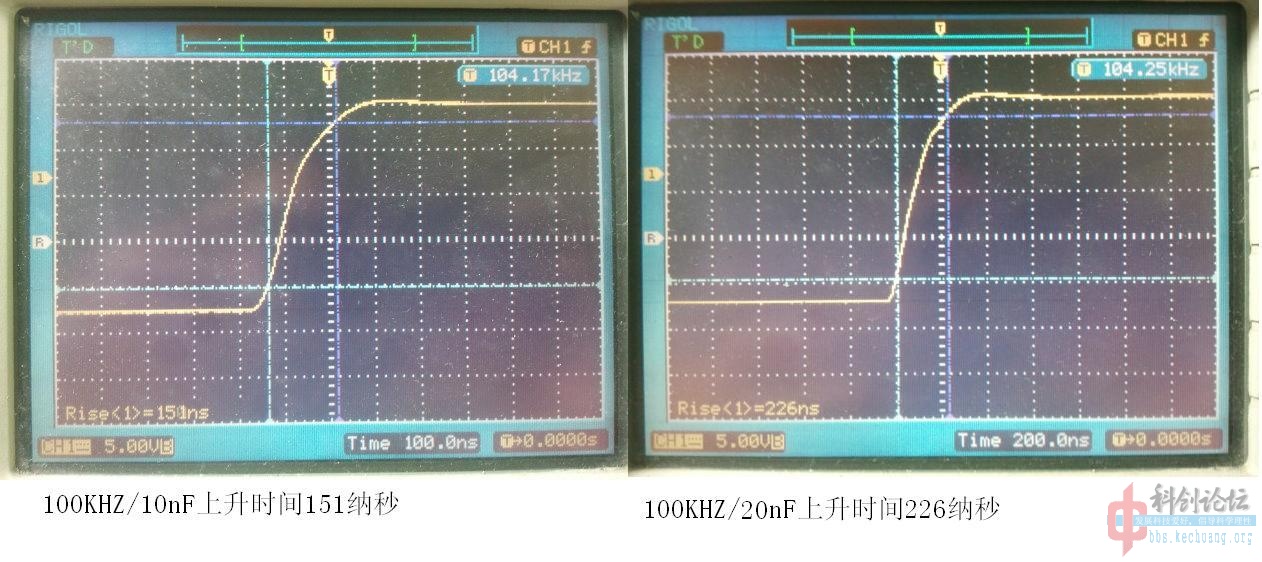

驱动波形图在下面,和ehco一样,我也实验了两种频率:40K和100K,我在图中详细标注了两种频率和负载下的上升和下降时间。

图中我也详细标注了各种频率和负载时的电源消耗。

图中还有一个详细的对比列表,由于ehco兄的电源消耗是相对于全桥的,我做的实验是单管的,所以列表中我的电源消耗都是按图中标注的4倍来标注。

以下是我的电路原理图,波形图,耗电和对比列表图。

![40KHZ上升时间.jpg]()

![40KHZ下降时间.jpg]()

![100KHZ上升时间.jpg]()

![100KHZ下降时间.jpg]()

![对比.jpg]()

从图和列表中可以看出,我的驱动在大负载时的驱动速度也超越ehco兄的,在小负载时虽然负载还是略大于ehco的,但驱动速度还是远超ehco兄,上升速度接近他的5倍!下降时间由于都用了外部电路加快关断,而不是靠驱动变压器来关断,所以下降时间差别不是很大,但还是快了不少。

再看耗电,ehco兄只标了24V820mA,不知是什么频率下的结果,所以就当是负载最重也就是100KHZ时的结果,从列表中看我的100KHZ/10nF 时的耗电是15.8V/195mA,电源消耗只是ehco的六分之一!

从图中的详细数据及列表可以看出,我的体积是他的几十分之一,速度将近5倍,耗电只有六分之一,综合起来看性能对比是多么的明显。由此看来,驱动性能并不是取决于多大的电流及功率余量,那么驱动性能有那些因素决定呢?——主要取决于驱动电路的峰值输出电流能力和驱动变压器的漏感,尤其以变压器的漏感最为重要。

我的原理图中栅极串联电阻最小是4.7欧,相对于此时的驱动峰值电流也就是5A而已,并不是很大,我只用了一个SO-8封装的贴片驱动IC,体积很小。但是变压器的漏感在这里就很关键了,这里我并没有给出变压器的漏感参数,测变压器的漏感意义并不大,因为漏感很难准确测量,测试频率不同,测量结果也不一样,测试时接触的好坏也影响测量结果。就算能准确测量,漏感一样的变压器,实际性能也不一定一样,甚至相差很远。决定变压器性能的是漏感占总电感的比列,漏感占总电感点比例越小,驱动性能越好。而什么又是决定变压器漏感的主要原因呢?——变压器的绕法!变压器的初次级平均距离越近,漏感越小。怎样减小初次级的距离?——减小线圈总厚度!怎样减小线圈的厚度?——线圈层数尽量少。层数少了绕不够圈数怎么办?——选窗口宽的磁芯。什么样的磁芯窗口宽?——环形磁芯。我的变压器就是用内径4.5mm外径9mm高6.5mm的铁氧体磁环做的,初级0.25mm漆包线15圈,次级0.25mm漆包线24圈都在同一层绕完,这样做出来的变压器漏感是最小的。还有很重要的一点是要在磁芯不饱和的前提下尽量减少圈数,当然磁通密度要留一定的余量,一般0.3特斯拉左右即可。

再来看ehco的驱动上升时间为何不理想,在这里我不想讨论除了驱动变压器以外的电路(ehco的外围电路比较复杂,不能乱加分析,我不知道他为何用如此复杂的电路),单从变压器上来分析。他用的是体积很大的罐形磁芯,而且从图中可以看出,线圈也基本上绕满了整个磁芯,初次级距离根本小不了,这样的绕法就算用三明治绕法,漏感也不会有多小,所以他的驱动上升时间达到了700多纳秒,100KHZ频率下这样的驱动速度,不要说硬开关,就是软开关都嫌慢。

最后分析一下,ehco兄的驱动为何如此耗电。和上面一样,我不想讨论他的外围电路(他自己也说了,某些元件温度有80度,而我的电路基本上没什么发热)。还是主要从变压器方面分析,大家应该要知道,铁氧体的损耗在频率和占空比都决定了的情况下,和体积是成正比的,从图中可以比较明显地看出,他的磁芯体积最少是我的50倍!这就好比用一辆大卡车来拉一辆小三轮车都拉得动的东西,能不耗油吗?初步估算一下,他的24V/820mA将近20W的功耗,光是变压器的损耗,应该就占百分之70——80,外围电路的损耗占百分之15——25,实际场效应管结电容上吸收到的能量最多也就百分之5.

200字以内,仅用于支线交流,主线讨论请采用回复功能。